P2020NXE2KFC ໄມໂຄຣໂປຣເຊສເຊີ MPU P2020E ET 1000/667 R2.1

♠ ລາຍລະອຽດຜະລິດຕະພັນ

| ຄຸນລັກສະນະຜະລິດຕະພັນ | ຄ່າຄຸນສົມບັດ |

| ຜູ້ຜະລິດ: | NXP |

| ປະເພດຜະລິດຕະພັນ: | ໄມໂຄຣໂປຣເຊສເຊີ - MPU |

| ຂໍ້ຈຳກັດການຂົນສົ່ງ: | ຜະລິດຕະພັນນີ້ອາດຈະຕ້ອງການເອກະສານເພີ່ມເຕີມເພື່ອສົ່ງອອກຈາກສະຫະລັດ. |

| RoHS: | ລາຍລະອຽດ |

| ຮູບແບບການຕິດຕັ້ງ: | SMD/SMT |

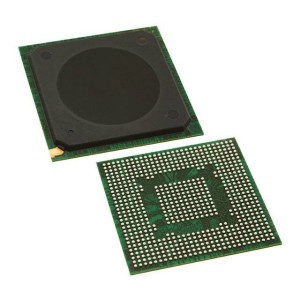

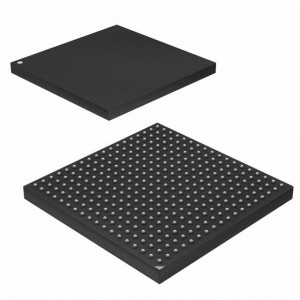

| ຊຸດ/ກໍລະນີ: | PBGA-689 |

| ຊຸດ: | P2020 |

| ຫຼັກ: | e500-v2 |

| ຈຳນວນຫຼັກ: | 2 ຫຼັກ |

| ຄວາມກວ້າງຂອງ Data Bus: | 32 ບິດ |

| ຄວາມຖີ່ໂມງສູງສຸດ: | 1 GHz |

| L1 Cache Instruction Memory: | 32 kB |

| L1 Cache Data Memory: | 32 kB |

| ແຮງດັນການສະຫນອງປະຕິບັດງານ: | 1.05 ວ |

| ອຸນຫະພູມປະຕິບັດຕໍາ່ສຸດທີ່: | - 40 ຄ |

| ອຸນຫະພູມການເຮັດວຽກສູງສຸດ: | + 125 ອົງສາ |

| ການຫຸ້ມຫໍ່: | ຖາດ |

| ຍີ່ຫໍ້: | NXP Semiconductors |

| ແຮງດັນ I/O: | 1.5 V, 1.8 V, 2.5 V, 3.3 V |

| ປະເພດຄໍາແນະນໍາ: | ຈຸດລອຍ |

| ປະເພດການໂຕ້ຕອບ: | ອີເທີເນັດ, I2C, PCIe, SPI, UART, USB |

| L2 Cache Instruction / Data Memory: | 512 kB |

| ປະເພດຫນ່ວຍຄວາມຈໍາ: | L1/L2 Cache |

| ຄວາມອ່ອນໄຫວດ້ານຄວາມຊຸ່ມຊື່ນ: | ແມ່ນແລ້ວ |

| ຈຳນວນ I/Os: | 16 I/O |

| ຊຸດປະມວນຜົນ: | QorIQ |

| ປະເພດຜະລິດຕະພັນ: | ໄມໂຄຣໂປຣເຊສເຊີ - MPU |

| ປະລິມານຊອງໂຮງງານ: | 27 |

| ໝວດຍ່ອຍ: | ໄມໂຄຣໂປຣເຊສເຊີ - MPU |

| ຊື່ການຄ້າ: | QorIQ |

| Watchdog Timers: | ບໍ່ມີໂມງຈັບເວລາ |

| ສ່ວນ # ນາມແຝງ: | 935319659557 |

| ນ້ຳໜັກໜ່ວຍ: | 0.185090 ອໍ |

ລາຍຊື່ຕໍ່ໄປນີ້ໃຫ້ພາບລວມຂອງຄຸນສົມບັດ P2020ຊຸດ:

• Dual ປະສິດທິພາບສູງ Power Architecture® e500 cores.

• ທີ່ຢູ່ 36-ບິດ

- ສະຫນັບສະຫນູນຈຸດເລື່ອນຄວາມຊັດເຈນສອງເທົ່າ

– ແຄດຄໍາແນະນໍາ 32-Kbyte L1 ແລະຂໍ້ມູນ 32-Kbyte L1cache ສໍາລັບແຕ່ລະຫຼັກ

- 800-MHz ຫາ 1.33-GHz ຄວາມຖີ່ໂມງ

• 512 Kbyte L2 cache ກັບ ECC. ຍັງ configurable ເປັນSRAM ແລະຄວາມຊົງຈໍາທີ່ເກັບໄວ້.

• ສາມ 10/100/1000 Mbps ປັບປຸງ Ethernet ສາມຄວາມໄວຕົວຄວບຄຸມ (etSECs)

- ການເລັ່ງ TCP/IP, ຄຸນນະພາບການບໍລິການ, ແລະ

ຄວາມສາມາດໃນການຈັດປະເພດ

– ຮອງຮັບ IEEE Std 1588™

- ການຄວບຄຸມການໄຫຼສູນເສຍ

– R/G/MII, R/TBI, SGMII

•ການໂຕ້ຕອບຄວາມໄວສູງສະຫນັບສະຫນູນ multiplexing ຕ່າງໆທາງເລືອກ:

– ສີ່ SerDes ກັບ 3.125 GHz multiplexed ທົ່ວຜູ້ຄວບຄຸມ

- ສາມ PCI Express interfaces

- ສອງ Serial RapidIO interfaces

- ສອງ SGMII ການໂຕ້ຕອບ

• ຕົວຄວບຄຸມ USB ຄວາມໄວສູງ (USB 2.0)

- ສະຫນັບສະຫນູນເຈົ້າພາບແລະອຸປະກອນ

- ການປັບປຸງການໂຕ້ຕອບການຄວບຄຸມແມ່ຂ່າຍ (EHCI)

- ການໂຕ້ຕອບ ULPI ກັບ PHY

• ປັບປຸງຕົວຄວບຄຸມແມ່ຂ່າຍດິຈິຕອນທີ່ປອດໄພ (SD/MMC)ປັບປຸງສ່ວນຕິດຕໍ່ຂ້າງຄຽງ Serial (eSPI)

• ເຄື່ອງຈັກຄວາມປອດໄພແບບປະສົມປະສານ

- ສະຫນັບສະຫນູນອະນຸສັນຍາປະກອບມີ SNOW, ARC4, 3DES, AES,RSA/ECC, RNG, ດຽວຜ່ານ SSL/TLS, Kasumi

- ການເລັ່ງ XOR

• 64-bit DDR2/DDR3 SDRAM ຄວບຄຸມຫນ່ວຍຄວາມຈໍາທີ່ມີສະຫນັບສະຫນູນ ECC

• Programmable interrupt controller (PIC) ສອດຄ້ອງກັບມາດຕະຖານ OpenPIC

• ສອງຕົວຄວບຄຸມ DMA ສີ່ຊ່ອງ

• ສອງຕົວຄວບຄຸມ I2C, DUART, ເຄື່ອງຈັບເວລາ

• ປັບປຸງຕົວຄວບຄຸມລົດເມທ້ອງຖິ່ນ (eLBC)

• 16 ສັນຍານ I/O ຈຸດປະສົງທົ່ວໄປ

• ອຸນຫະພູມຈຸດປະຕິບັດການ

• 31 × 31 ມມ 689-pin WB-TePBGA II (ສາຍພັນທະບັດBGA ພາດສະຕິກເສີມອຸນຫະພູມ)